# POWER LINE MODEMS & APPLICATIONS

1st EDITION

**SEPTEMBER 1994**

| USE IN LIFE SUPPORT DEVICES OR SYSTEMS MUST BE EXPRESSLY AUTHORIZED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SGS-THOMSON PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF SGS-THOMSON Microelectronics. As used herein:                                                                                                                                                                                                                                                                                                                                                                                                 |

| <ol> <li>Life support devices or systems are those which (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided with the product, can be reasonably expected to result in significant injury to the user.</li> <li>A critical component is any component of a life support device or system whose failure to perform can reasonably be expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.</li> </ol> |

# **TABLE OF CONTENTS**

| INTRODUCTION                                                                      | Page 4                   |

|-----------------------------------------------------------------------------------|--------------------------|

| GENERAL INDEX                                                                     | 7                        |

| ST7536 DATASHEETS                                                                 | Ş                        |

| ST7536 APPLICATION NOTE                                                           | 21                       |

| ST7537 DATASHEET                                                                  | 75                       |

| ST7537 APPLICATION NOTE                                                           | 87                       |

| ST7537 STARTER KIT                                                                | 163                      |

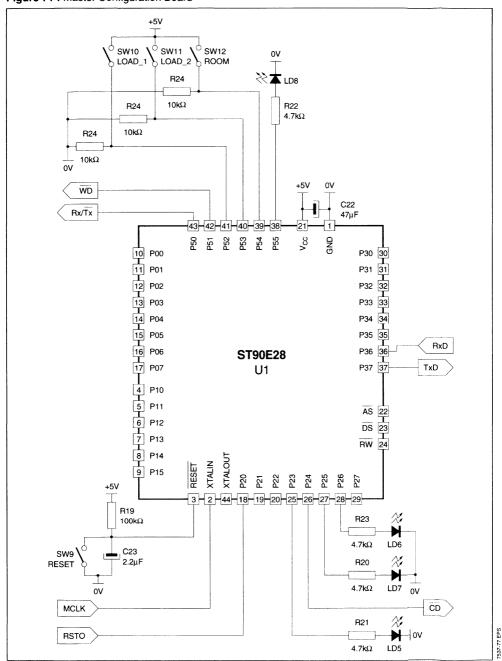

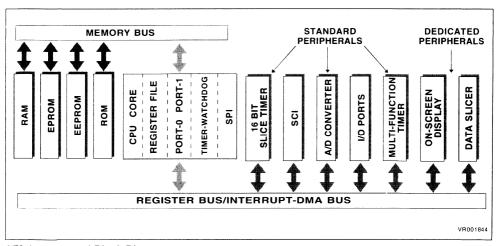

| ST9 FAMILY - 8/16 BIT MCUs - INTRODUCTION                                         | 171<br>173               |

| ST9 FAMILY OVERVIEW                                                               | 175                      |

| DEVELOPMENT TOOLS  - ST9 STARTER KIT  - ST9-GNU TOOLCHAIN  - ST9 APPLICATION NOTE | 179<br>181<br>185<br>187 |

| TRIAC APPLICATION NOTES                                                           | 213                      |

# **Dedicated Modem Chip Targets Home Automation Systems**

Sending data over 220V/110V power lines, the ST7537 Home Automation modem lets appliances communicate without extra cabling.

by Joël Huloux & Jérôme Gilbert

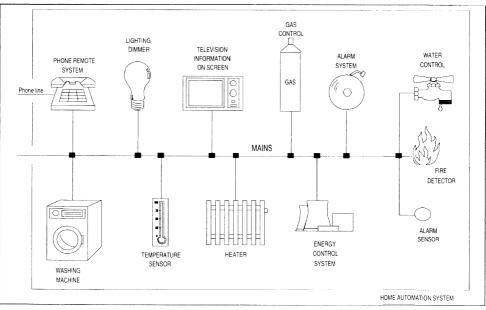

In the latest generation of home automation systems, appliances can exchange information by transmitting data over the domestic mains wiring. As a result there is no need to install extra control cables and appliances can be connected to the "network" simply by plugging them into the nearest wall socket. Apart from the obvious saving in installation cost, this virtual network also makes modification and enhancement very simple since new devices just have to be plugged into a wall socket to be instantly connected to the network.

What makes these systems feasible is a new dedicated modem integrated circuit, the SGS-THOMSON ST7537 Home Automation Modem IC, developed specifically for this new high volume consumer market as part of a European Community "ESPRIT" project on domestic automation.

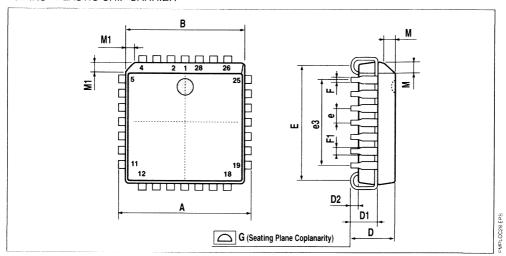

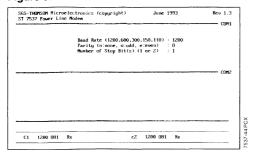

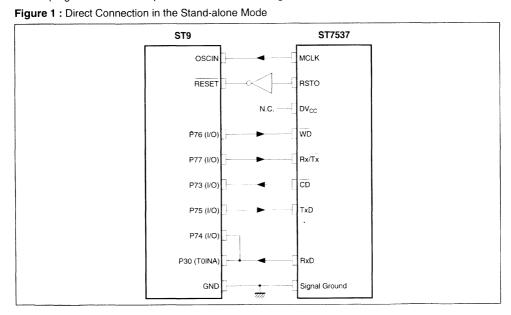

mation applications, the SGS-THOM-SON Microelectronics ST7537 Home Automation Modem IC sends data at 1200bps over 220/110V power lines using a 132.45kHz carrier, this eliminating the need for extra cabling. A PLCC28 package is used.

# THE MODEM CHIP

Fabricated in analog CMOS technology, the ST7537 sends and receives data at 1200bps in half duplex mode using a carrier frequency of 132.45kHz, complying with Europe's CENELEC ES 50065 standard (which specifies the use of band 125kHz to 140kHz carrier frequencies for home automation) and US FCC regulations.

Frequency-shift keying is used for transmission, a fundamental design choice that makes it possible to achieve rugged transmission in a very noisy electrical environment at an affordable cost for high-

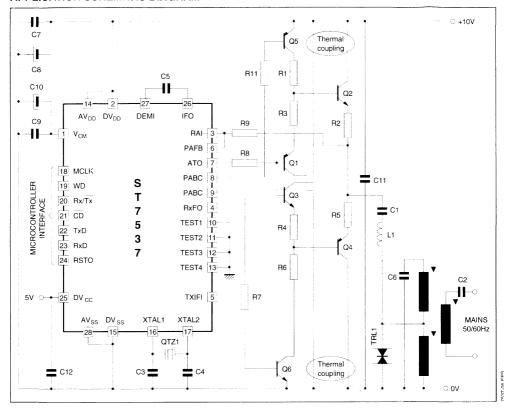

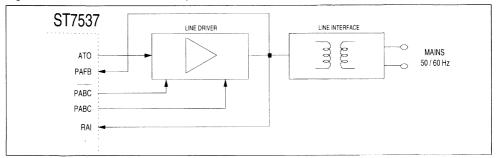

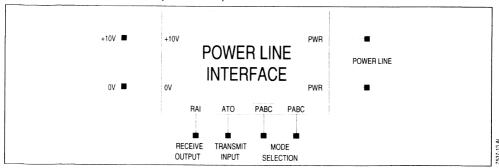

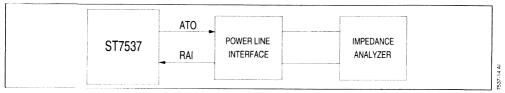

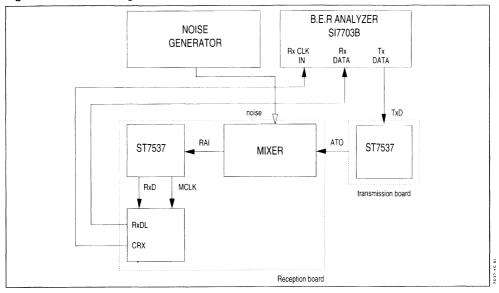

Inside the ST7537 are all of the basic functions needed in a power line modem, plus carrier detection and watchdog functions. The only external components needed are a transformer and a simple line driver.

volume consumer markets. Among the alternatives, amplitude-shift keying is too susceptible to noise and Spread Spectrum, though theoretically more reliable, requires complex and costly circuits. Moreover, field trials in a critical remote utility meter reading application have proven the dependability of the SGS-THOMSON approach.

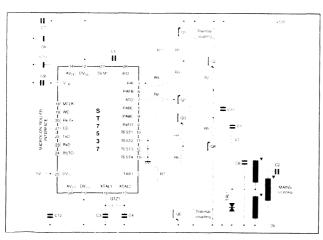

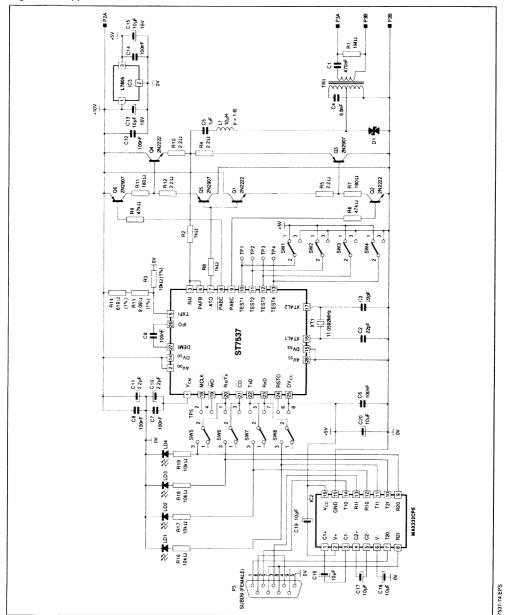

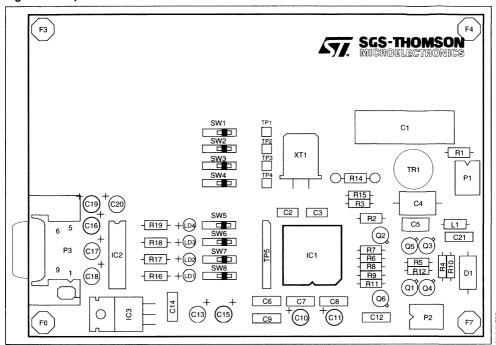

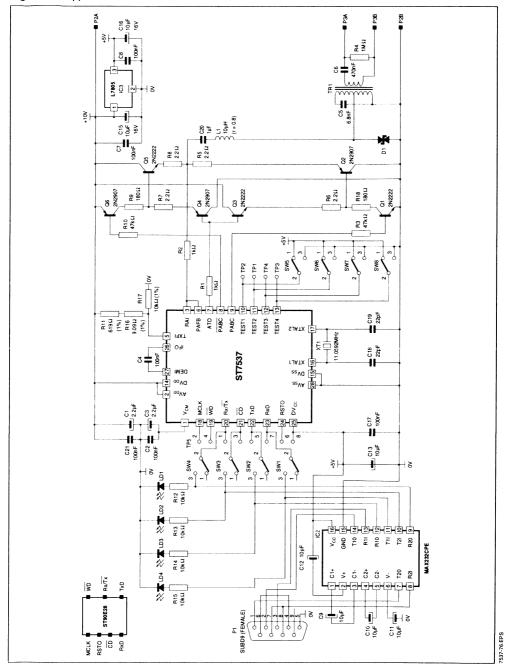

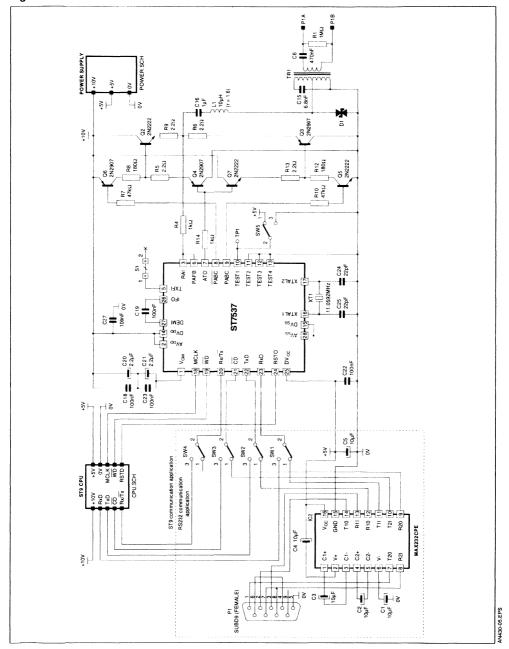

Included on the chip are all of the functional blocks necessary for the transmission and reception of data over power lines. In addition to this IC the only external components needed are a line driver and a transformer, plus, of course, the microcontroller that prepares and interprets message data. The photo shows a complete module made by Landis & Gyr, the schematic of which is given below. In this module the ST7537 die is mounted directly on the under side of the board without a conventional package, though the de-

This compact modem module designed by Landis & Gyr mounts the ST7537 die directly on the underside of the board. Surface mounting transistors are used to make the line driver.

vice is also supplied in a PLCC28 package.

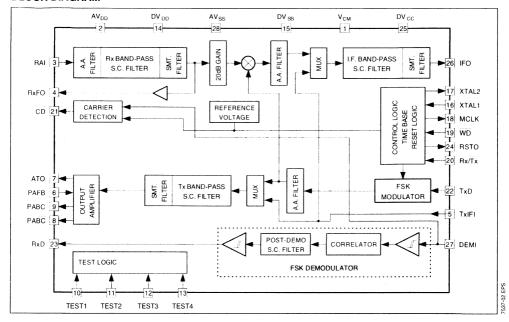

Transmit data enters the FSK modulator asynchronously with a nominal intra-message data rate of 1200bps. Inside the modulator the data is transformed into two frequencies (133.05kHz for a "0" and 131.85kHz for a "1"), derived from an inexpensive 11.0592 MHz crystal.

The modulated signal from the FSK modulator is filtered by a switched-capacitor bandpass filter (TX bandpass) to limit the output spectrum and to reduce the level of harmonic components. The final stage of the transmit path consists of an operational amplifier which needs a feedback signal from the power amplifier.

In the receive section, the incoming signal is applied at the RAI input (with a sensitivity of 10mV) where it is first filtered by a switched-capacitor bandpass filter with a pass band of around 12kHz, centered on the carrier frequency. The output of the filter is amplified by a 20dB gain stage which provides symmetrical limitation for overvoltages. The resulting signal is downconverted by a mixer which receives a local oscillator synthesized by the FSK modulator block.

Finally, an intermediate frequency bandpass filter whose central frequency is 5.4kHz improves the signal-to-noise ratio before entering the FSK demodulator. The coupling of the intermediate frequency filter output to the FSK demodulator input is made by an external capacitor which cancels the receive path offset.

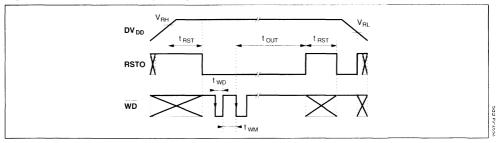

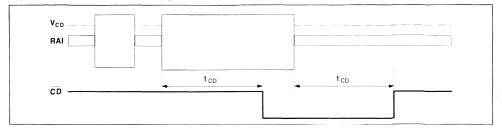

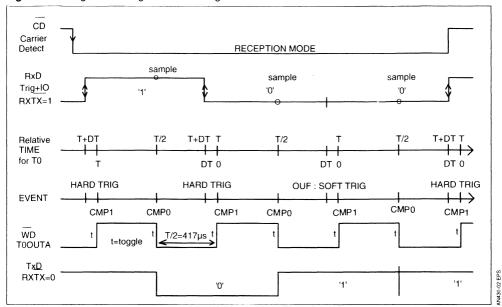

In the ST7537 there are two important additional functions: the carrier detector and the watchdog. Carrier detection is needed because in practically all applications more than two appliances will be connected to the power line. Before attempting to transmit an appliance must first check that there is no carrier present, and

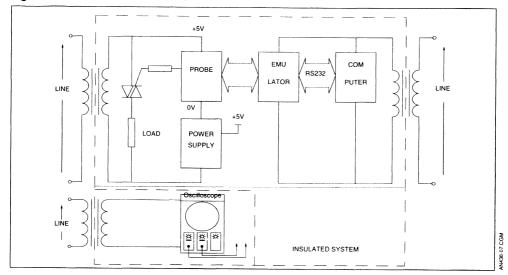

Schematic of the application board shown in the photo above.

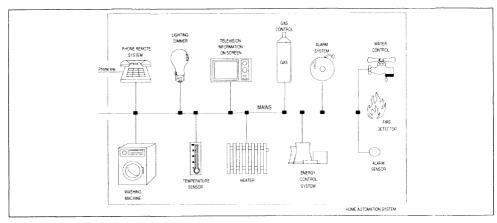

In a typical home each appliance or device will have an ST7537 module and communicate with other devices using the power cable.

if there is, it must wait and retry later.

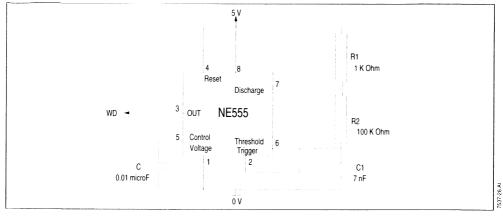

The watchdog function is provided to ensure that the modem's control micro is functioning correctly. Software in the micro must include instructions that send a pulse to the watchdog input of the ST7537 at least once every 1.5 seconds. If no negative transition is observed at this input for 1.5s a reset signal is generated to restart the micro. This watchdog monitor scheme ensures that any disruptions caused by glitches are quickly corrected.

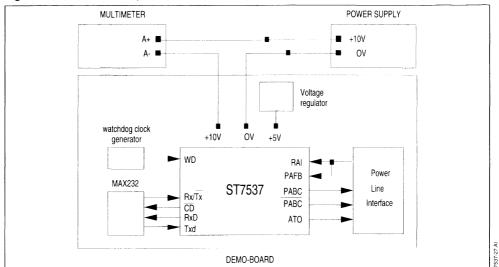

During full operation the ST7537 dissipates less than 300mW. Supplies of 10V and 5V are used.

#### THE HOME SYSTEM PROJECT

SGS-THOMSON Microelectronics is a member of an ES-PRIT project on home automation, together with EDF (Electricité de France, the French electricity authority), Landis & Gyr, Daimler

Benz, Merlin Gerin and Thomson Consumer Electronics. These industrial partners have built a platform for development tools that work with a common protocol, called Home System (HS).

One of the partners, Landis & Gvr. already uses the new ST7537 modem chip in a new family of home automation products. Thanks to products like these we enter a new era of appliances that are not only smart, but they communicate with each other, too. A typical household scenario is shown above, where various appliances, sensors, utility controls, a telephone interface and a TV screen display are all connected to the power line using Landis & Gyr modules.

If this automated house catches fire the appropriate detector will send a warning message over the power line. This will be picked up by the gas control which can cut off the gas supply, by an alarm

system that can alert anyone in the house, and even by the telephone interface that can call the emergency services.

The telephone interface also allows the householder to give instructions to appliances from outside. You might, for example, phone home and tell the air conditioner to precool certain rooms at a specified time.

Where there is a limit on energy consumption, or where demand energy pricing is used (now that the technology is available this is likely to be applied extensively in future) various appliances can negotiate power requirements through an energy control system. For example, a washing machine can agree with the heating system when it can start a cycle to avoid sudden and unnecessary peaks of demand.

1993 SGS-THOMSON Microelectronics, all rights reserved. The cover illustration appeared first in the magazine Elektronik Informationen.

# ----- GENERAL INDEX -----

| Datasheets and<br>Application Notes | Function                                                                | Page |

|-------------------------------------|-------------------------------------------------------------------------|------|

| ST7536                              | Power Line Modem                                                        | 11   |

| AN653                               | ST7536 Application Note                                                 | 23   |

| ST7537                              | Home Automation Modem                                                   | 77   |

| AN655                               | ST7537 Power Line Modem Application                                     | 89   |

| ST7537 Starter Kit                  | ST7537 Power Line Modem                                                 | 165  |

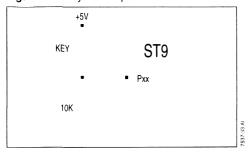

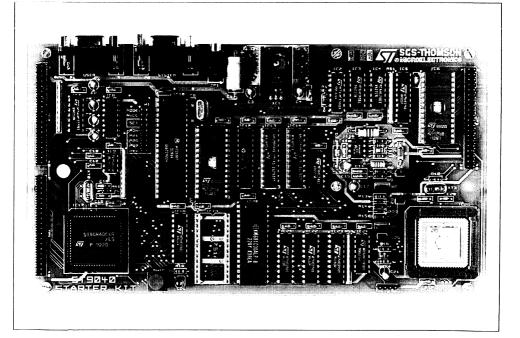

| ST9 Starter Kit                     | Evaluation Kit for ST9 MCU Family                                       | 181  |

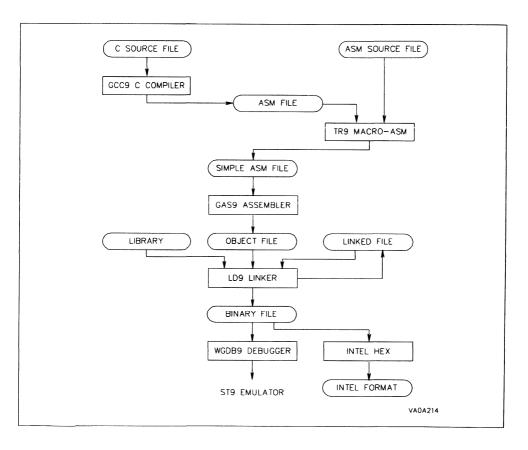

| ST9-GNU<br>TOOLCHAIN                | C Complier, Assembler, Linker and Source Debugger for ST9 MCU Family    | 185  |

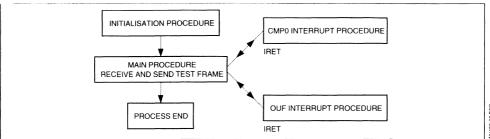

| AN430                               | Synchronous Power Line Modem Communication with ST9 Multifunction Timer | 187  |

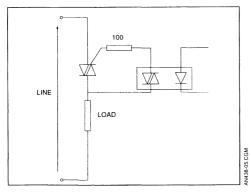

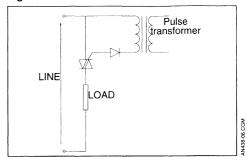

| AN328                               | Protect your TRIAC                                                      | 215  |

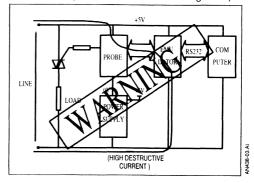

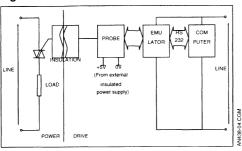

| AN438                               | TRIAC + MICROCONTROLLER Safety Precautions for Development Tool         | 219  |

|  |  | , |

|--|--|---|

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

# **ST7536 DATASHEET**

# POWER LINE MODEM

- HALF DUPLEX SYNCHRONOUS FSK MODEM

- Two programmable channels for 600bps data rate

- Two programmable channels for 1200bps data rate

- AUTOMATICALLY TUNED Rx AND Tx FILTERS

- TX CARRIER FREQUENCIES SYNTHESIZED FROM EXTERNAL CRYSTAL

- LOW DISTORTION Tx SIGNAL (S/H2 ≥ 50dB)

- AUTOMATIC LEVEL CONTROL ON Tx SIGNAL

- Rx SENSITIVITY: 2mV<sub>RMS</sub> (600bps) 3mV<sub>RMS</sub> (1200bps)

- Rx CLOCK RECOVERY

- POWER-DOWN MODE

- SUITABLE TO APPLICATION IN ACCORD-ANCE WITH DH028/29 ENEL, EN50065-1 CENELEC AND FCC SPECIFICATIONS

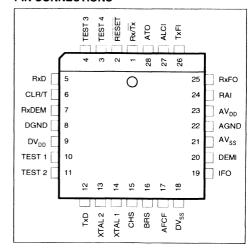

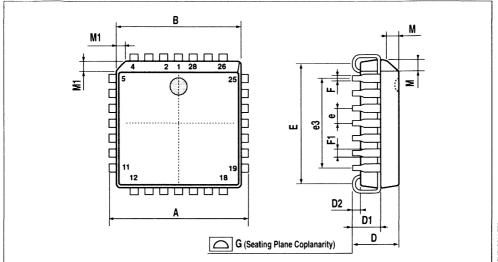

# PIN CONNECTIONS

# DESCRIPTION

The ST7536 is a half duplex synchronous FSK MODEM designed for power line communication network applications.

It operates from a dual power supply +5V and -5V, and requires an external interface for the coupling to the power line. It offers two programmable data rate with two programmable channels each.

May 1993

# PIN DESCRIPTION

| Pin<br>Name | Pin<br>Number | Pin<br>Type | Description                                                                                                    |

|-------------|---------------|-------------|----------------------------------------------------------------------------------------------------------------|

| Rx/Tx       | 1             | Digital     | Rx or Tx mode selection input                                                                                  |

| RESET       | 2             | Digital     | Logic reset and power-down mode input. Active when low.                                                        |

| TEST4       | 3             | Digital     | Test input which selects the Tx band-pass filter input (TxFI) when high.                                       |

| TEST3       | 4             | Digital     | Test input which gives an access to the clock recovery input stage. This input is selected when TEST1 is high. |

| RxD         | 5             | Digital     | Synchronous receive data output                                                                                |

| CLR/T       | 6             | Digital     | Rx or Tx clock according to the functional mode                                                                |

| RxDEM       | 7             | Digital     | Demodulated data output                                                                                        |

| DGND        | 8             | Supply      | Digital ground                                                                                                 |

| DVDD        | 9             | Supply      | Digital positive supply voltage : 5V ± 5%                                                                      |

| TEST1       | 10            | Digital     | Test input which cancels the Tx to Rx mode automatic switching and validates TEST3 input. Active when high.    |

| TEST2       | 11            | Digital     | Test input which reduces the Tx to Rx mode automatic switching time. Active when high.                         |

| TxD         | 12            | Digital     | Transmit data input                                                                                            |

| XTAL2       | 13            | Digital     | Crystal oscillator output                                                                                      |

| XTAL1       | 14            | Digital     | Crystal oscillator input                                                                                       |

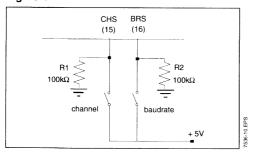

| CHS         | 15            | Digital     | Channel selection input                                                                                        |

| BRS         | 16            | Digital     | Baud rate selection input                                                                                      |

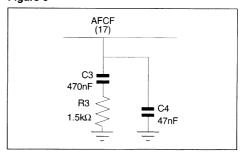

| AFCF        | 17            | Analog      | Automatic frequency control output for connecting compensation network.                                        |

| DVSS        | 18            | Supply      | Digital negative supply voltage : -5V $\pm$ 5%                                                                 |

| IFO         | 19            | Analog      | Intermediate frequency filter output                                                                           |

| DEMI        | 20            | Analog      | FSK demodulator input                                                                                          |

| AVSS        | 21            | Supply      | Analog negative supply voltage : -5V $\pm$ 5%                                                                  |

| AGND        | 22            | Supply      | Analog ground: 0V                                                                                              |

| AVDD        | 23            | Supply      | Analog positive supply voltage : 5V ± 5%                                                                       |

| RAI         | 24            | Analog      | Receive analog input                                                                                           |

| RxFO        | 25            | Analog      | Receive filter output                                                                                          |

| TxFI        | 26            | Analog      | Transmit filter input (selected when TEST4 is high)                                                            |

| ALCI        | 27            | Analog      | Automatic level control input                                                                                  |

| ATO         | 28            | Analog      | Analog transmit output                                                                                         |

230-01-100

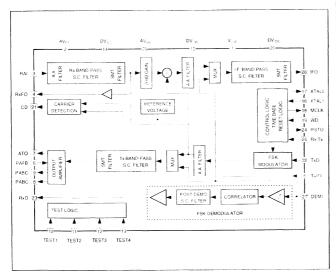

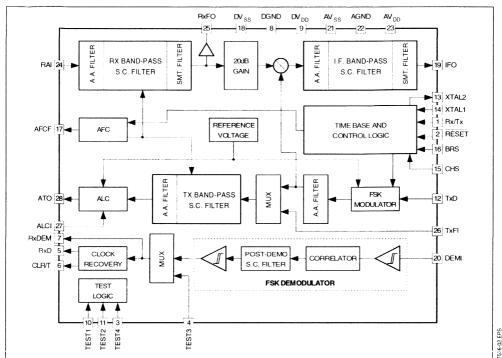

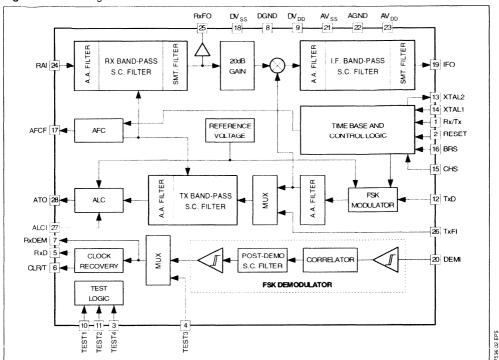

# **BLOCK DIAGRAM**

# TRANSMIT SECTION

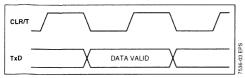

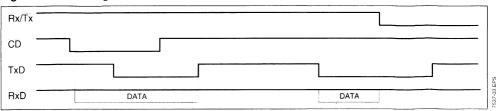

The transmit mode is set when Rx/Tx = 0, if Rx/Tx is held at 0 longer than 3 seconds, then the device switches automatically in the Rx mode. A new activation of the Tx mode requires Rx/Tx to be returned to 1 for a minimum 2 microsecond period before being set to 0.

The Transmit Data (TxD) is sampled on a positive edge of CLR/T which delivers the transmit bit clock when the transmit mode is selected. This data enters a FSK modulator whose two basic frequencies are selected by the Baud Rate Selection pin (BRS) and the Channel Selection pin (CHS) according to the Table 1.

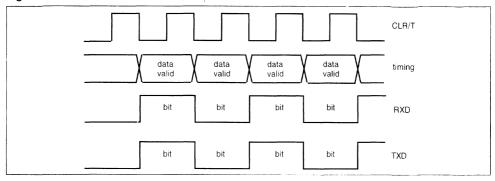

Figure 1: Tx Data Input Timing

#### Table1

|          | BRS | снѕ | Baud Rate<br>(Baud) | Tx Frequencies (kHz)<br>TxD=1 - TxD=0 |

|----------|-----|-----|---------------------|---------------------------------------|

|          | 0   | 0   | 600                 | 81.75 - 82.35                         |

| The same | 0   | 1   | 600                 | 67.2 - 67.8                           |

| ĺ        | 1   | 0   | 1200                | 71.4 - 72.6                           |

|          | 1   | 1   | 1200                | 85.95 - 87.15                         |

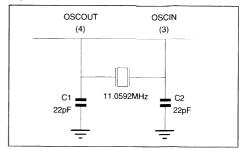

These frequencies are synthesized from a 11.0592MHz crystal oscillator; their precision is the same as the crystal one's (100 ppm).

The modulated signal coming out of the FSK modulator is filtered by a switched-capacitor band-pass filter (Tx band-pass) in order to limit the output spectrum and to reduce the level of harmonic components.

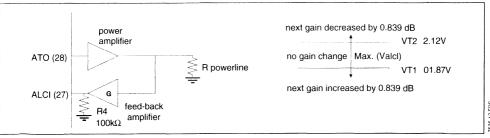

The output stage of the Tx path consists of an Automatic Level Control (ALC) system which keeps the output signal (ATO) amplitude independant of the line impedance variations. This ALC is a variable gain system (with 32 discrete values) controlled by an analog feed-back signal ALCI. The ALC

gain range is 0dB to -26dB and gain change is clocked at 7200Hz. Gain steps are of magnitude 0.84dB typically.

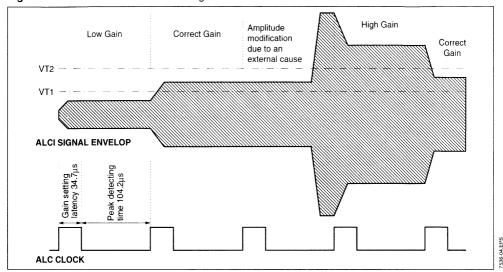

A period of this clock is decomposed into a 34.7 $\mu$ s gain settling latency and a 104.2 $\mu$ s peak detecting time. The gain change is related to the result of a peak detection obtained by making a direct com-

parison of ALCI maximum value (during detecting time) with two threshold voltages  $V_{T1}$  and  $V_{T2}$ .

- max (VALCI)

V<sub>T1</sub> The next gain is increased by 0.84dB

- V<sub>T1</sub> ≤ max (VALCI)≤ V<sub>T2</sub> No gain change

- V<sub>T2</sub> < max (VALCI) The next gain is decreased by 0.84dB.

Figure 2: Automatic Level Control Timing Chart

# RECEIVE SECTION

The receive section is active when Rx/Tx = 1.

The baud rate and channel selection is also made according to Table 1.

The Rx signal is applied on RAI with a common mode voltage of 0 volt and filtered by a band-pass switched capacitor filter (Rx band-pass) centered on the received carrier frequency and whose bandwidth is around 6 kHz. The input voltage range on RAI is 2mV<sub>RMS</sub> - 2V<sub>RMS</sub>.

The Rx filter output is amplified by a 20dB gain stage which provides symmetrical limitations for large voltage. The resulting signal is down-converted by a mixer which receives a local oscillator synthesized by the FSK modulator block. Finally an intermediate frequency band-pass filter (IF band-pass) whose central frequency is 2.7kHz when BRS = 0 and 5.4kHz when BRS = 1 improves the signal to noise ratio before entering the FSK demodulator. The coupling of the intermediate frequency filter output (IFO) to the FSK demodulator input (DEMI) is made by an external capacitor C5

$(1\mu F~\pm 10\%,~10V)$  which cancels the Rx path offset voltage.

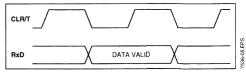

A clock recovery circuit extracts the receive clock (CLR/T) from the demodulated output (RxDEM) and delivers synchronous data (RxD) on the positive edge of CLR/T.

Figure 3: Rx Data Output Timing

# ADDITIONAL DIGITAL AND ANALOG FUNC-

A reset intput (RESET) initializes the device.

When RESET = 0, the device is in power-down mode and all the internal logic is reset. When RESET = 1, the device is active.

A time base section delivers all the internal clocks

from a crystal oscillator (11.0592MHz). The crystal is connected between XTAL1 and XTAL2 pins and needs two external capacitors C3 and C4 depending on the crystal characteristic typically 22pF ±10% for proper operation. It is also possible to provide directly the clock on pin XTAL1; in this case C3 and C4 should be removed.

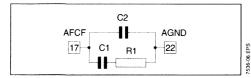

An Automatic Frequency Control (AFC) Section adjusts the central frequency of Rx and Tx bandpass filter to the carrier central frequency. The stability of the AFC loop is ensured by an external compensation network C1 (470nF ±10%, 10V), C2  $(47nF \pm 10\%, 10V)$  and R1  $(1.5k\Omega \pm 5\%)$  connected to pin AFCF.

Figure 4: Automatic Frequency Loop Filter

# **TESTING FEATURES**

- An additionnal amplifier allows the observation of the Rx band-pass filter output on pin RxFO.

- A direct input to the Tx band-pass filter (TxFI) is available and selected when TEST4 = 1.

- The 3 second normal duration of the Tx to Rx mode automatic switching is reduced to 1.48ms when TEST2 = 1.

- When TEST1 = 1 the Tx to Rx mode automatic switching is desactivated and the functional mode of the circuit is controlled by Rx/Tx as

follow: when Rx/Tx = 0 the circuit is transmitting continuously, when Rx/Tx = 1 the clock recovery block is disconnected from the FSK demodulator for testing purpose, in this configuration TEST 3 is the data input of the clock recovery block, RXDEM follow TEST3 and RxD delivers the resynchronized data.

# POWER SUPPLIES WIRING AND DECOUPLING **PRECAUTIONS**

The ST7536 has two positive power supply pins, two negative power supply pins and two ground pins in order to separate internal analog and digital supplies. The analog and digital terminals of each supply pair must be connected together externally and require special routing precautions in order to get the best receive sensitivity performances. The three major routing requirements are:

- The ground impedance should be as low as possible, for this purpose the AGND an DGND terminals can be connected via a local plane.

- The positive and negative power supplies (AV<sub>DD</sub>). DV<sub>DD</sub>, AV<sub>SS</sub>, DV<sub>SS</sub>) should be star-connected, avoiding common current path for the digital and analog power supplies terminals.

- Five decoupling capacitors located as close as possible to the power supply terminals should be used. Two 2.2µF tantalum and two 100nF ceramic capacitors perform the main decoupling function in the vicinity of the analog power supplies and a 100nF ceramic capacitor in the vicinity of the positive digital power supply is used to reduce the high frequency perturbations generated by the logic part of the circuit.

#### ABSOLUTE MAXIMUM RATINGS

| Symbol                             | Parameter                     | Value                                        | Unit |

|------------------------------------|-------------------------------|----------------------------------------------|------|

| $AV_{DD}/DV_{DD}$                  | Positive Supply Voltage (1)   | -0.3, +7                                     | ٧    |

| AV <sub>SS</sub> /DV <sub>SS</sub> | Negative Supply Voltage (1)   | -7, +0.3                                     | ٧    |

| V <sub>AGND/DGND</sub>             | Voltage between AGND and DGND | -0.3, +0.3                                   | ٧    |

| Vı                                 | Digital Input Voltage         | DGND-0.3, DV <sub>DD</sub> +0.3              | ٧    |

| Vo                                 | Digital Output Voltage        | DGND-0.3, DV <sub>DD</sub> +0.3              | V    |

| lo                                 | Digital Output Current        | -5, +5                                       | mA   |

| Vı                                 | Analog Input Voltage          | AV <sub>SS</sub> -0.3, AV <sub>DD</sub> +0.3 | V    |

| Vo                                 | Analog Output Voltage         | AV <sub>SS</sub> -0.3, AV <sub>DD</sub> +0.3 | V    |

| lo                                 | Analog Output Current         | -5, +5                                       | mA   |

| PD                                 | Power Dissipation             | 500                                          | mW   |

| Toper                              | Operating Temperature         | - 25, + 70                                   | °C   |

| T <sub>stg</sub>                   | Storage Temperature           | - 65, + 150                                  | °C   |

- Notes: 1. The voltages are referenced to AGND and DGND.

- 2. Latch-up problems can be overcome with 2 reverse biased schottky diodes connected respectively between A/DV<sub>DD</sub> & A/DGND and A/DVss & A/DGND.

- 3. Absolute maximum ratings are values beyond which damage to device may occur. Functional operation under these conditions is not implied.

7536-02.TBL

# **GENERAL ELECTRICAL CHARACTERISTICS**

The test conditions are  $A/DV_{DD} = +5V$ ,  $A/DV_{SS} = -5V$ , A/DGND = 0V,

T<sub>amb</sub> = -10 to 70°C unless otherwise specified

| Symbol                              | Parameter                          | Test Conditions                            | Min.  | Тур  | Max   | Unit |

|-------------------------------------|------------------------------------|--------------------------------------------|-------|------|-------|------|

| AV <sub>DD</sub> /DV <sub>DD</sub>  | Positive Supply Voltage            |                                            | 4.75  | 5    | 5.25  | ٧    |

| AV <sub>SS</sub> /DV <sub>SS</sub>  | Negative Supply Voltage            |                                            | -5.25 | -5   | -4.75 | V    |

| Al <sub>DD</sub> + DI <sub>DD</sub> | Positive Supply Current in Tx Mode | RESET = 1, RX/Tx = 0                       |       | 30   | 35    | mA   |

| Al <sub>DD</sub> + Dl <sub>DD</sub> | Positive Supply Current in Rx Mode | RESET = 1, RX/Tx = 1                       |       | 29   | 34    | mA   |

| Alss + Dlss                         | Negative Supply Current in Tx Mode | RESET = 1, RX/Tx = 0                       | - 34  | - 29 |       | mA   |

| Alss + Dlss                         | Negative Supply Current in Rx Mode | RESET = 1, RX/Tx = 1                       | - 33  | - 28 |       | mA   |

| Al <sub>DD</sub> + Dl <sub>DD</sub> | Positive Power-down Current        | RESET = 0, RX/Tx = 1                       |       |      | 1.2   | mA   |

| Alss + Dlss                         | Negative Power-down Current        | XTAL1 = 1                                  | - 1.2 |      |       | mA   |

| V <sub>IH</sub>                     | High Level Input Voltage           | Digital inputs except XTAL1                | 2.2   |      |       | ٧    |

| V <sub>IL</sub>                     | Low Level Input Voltage            | Digital inputs                             |       |      | 0.8   | V    |

| V <sub>OH</sub>                     | High Level Output Voltage          | Digital outputs, I <sub>OH</sub> = - 400μA | 2.4   |      |       | V    |

| V <sub>OL</sub>                     | Low Level Output Voltage           | Digital outputs, I <sub>OL</sub> = 1.6mA   |       |      | 0.4   | V    |

| VIH                                 | High Level Input Voltage           | XTAL1 input                                | 3.6   |      |       | ٧    |

| DC                                  | XTAL1 Clock Duty Cycle             | External clock                             | 40    |      | 60    | %    |

# TRANSMITTER ELECTRICAL CHARACTERISTICS

The test conditions are  $A/DV_{DD} = +5V$ , A/DGND = 0V,  $A/DV_{SS} = -5V$ ,

$T_{amb} = -10 \text{ to } +70^{\circ}\text{C}$  unless othewise specified

| Symbol           | Parameter                               | Test Conditions                                                                 | Min.     | Тур         | Max  | Unit            |

|------------------|-----------------------------------------|---------------------------------------------------------------------------------|----------|-------------|------|-----------------|

| V <sub>TAC</sub> | Max Carrier Output AC Voltage           | $R_L = 2k\Omega$ , $V_{ALCI} < V_{T1}$                                          | 2.8      | 3.2         | 3.7  | V <sub>PP</sub> |

| HD2              | Second Harmonic Distortion              | $R_L = 2k\Omega$ , $V_{ALCI} < V_{T1}$                                          |          |             | 0.32 | %               |

| FD               | FSK Peak-to-peak Deviation              | BRS = 0<br>BRS = 1                                                              |          | 600<br>1200 |      | Hz<br>Hz        |

| TRxTx            | Carrier Activation Time                 | After Rx/Tx 1 → 0 transition                                                    |          |             | 1    | ms              |

| TALC             | Carrier Stabilisation Time              | ALC maximum settling time 32 gain steps                                         |          |             | 5    | ms              |

| DRNG             | ALC Dynamic Range                       |                                                                                 | 25       | 26          | 27   | dB              |

| VT1              | ALC Low Threshold Voltage               |                                                                                 | 1.81     | 1.87        |      | ٧               |

| VT2              | ALC High Threshold Voltage              |                                                                                 |          | 2.12        | 2.18 | ٧               |

| GST              | ALC Gain Step                           |                                                                                 |          | 0.84        |      | dB              |

| PSRR1<br>PSRR2   | Power supply rejection ratio on ATO (1) | $V_{IN} = 200 \text{mV}_{PP}$ , $f_{IN} = 50 \text{Hz}$ on $V_{DD}$ or $V_{SS}$ | 35<br>10 |             |      | dB<br>dB        |

Note 1 : This characteristic is guaranteed by correlation.

7536-04.TBL

# RECEIVER ELECTRICAL CHARACTERISTICS

The test conditions are  $A/DV_{DD} = +5V$ , A/DGND = 0V,  $A/DV_{SS} = -5V$ ,

$T_{amb} = -10 \text{ to } +70^{\circ}\text{C}$  unless othewise specified

| Symbol                               | Parameter                                             | Test Conditions                                                                                                                                                                                                     | Min      | Тур                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Max                                  | Unit              |

|--------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------|

| VIN                                  | Maximum Input Signal                                  |                                                                                                                                                                                                                     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2                                    | V <sub>RMS</sub>  |

| R <sub>IN</sub>                      | Input Impedance                                       |                                                                                                                                                                                                                     | 100      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      | kΩ                |

| RCJ                                  | Recovered Clock Jitter                                | Percentage of the nominal clock                                                                                                                                                                                     | - 5      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | + 5                                  | %                 |

| PSRR1<br>PSRR2                       | Power supply rejection ratio on RxFO (1)              | $V_{IN} = 200 \text{mV}_{PP}, f_{IN} = 50 \text{Hz}$<br>on $V_{DD}$ or $V_{SS}$                                                                                                                                     | 35<br>10 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      | dB<br>dB          |

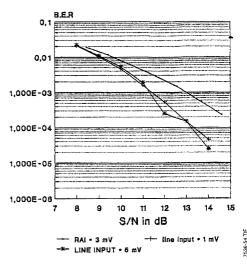

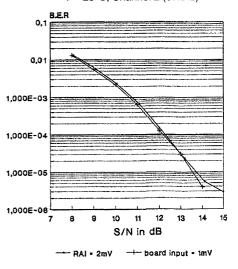

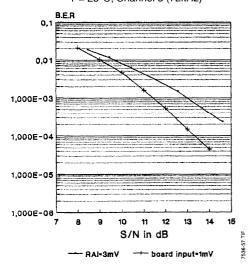

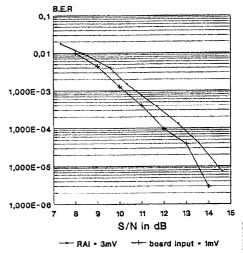

| V <sub>INO</sub><br>V <sub>IN1</sub> | Rx sensitivity (1)                                    | Typical measured BER < 10 <sup>-5</sup><br>BRS = 0<br>BRS = 1                                                                                                                                                       |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2<br>3                               | mV <sub>RMS</sub> |

| BER1<br>BER2                         | Bit error rate at minimum Rx signal (1)               | White Noise, S/N = 15dB<br>RAI = 2mV <sub>RMS</sub> , BRS = 0<br>RAI = 3mV <sub>RMS</sub> , BRS = 1                                                                                                                 |          | 2 · 10 <sup>-5</sup><br>3 · 10 <sup>-4</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10 <sup>-3</sup>                     |                   |

| BER3                                 | Bit error rate at maximum Rx signal (1)               | RAI = $2V_{RMS}$ , White Noise S/N = $25dB$                                                                                                                                                                         |          | 10 <sup>-7</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10 <sup>-3</sup>                     |                   |

| BER4                                 | Bit error rate at medium Rx signal (1)                | RAI= 0.6V <sub>RMS</sub> , S/N= 15dB                                                                                                                                                                                |          | 10 <sup>-6</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10 <sup>-3</sup>                     |                   |

| BER5                                 | Bit error rate with impulsive noise (1)               | RAI = 90mV <sub>RMS</sub> , N = 5V <sub>PP</sub> pulse wave, f = 100Hz, duty cycle = 10%                                                                                                                            |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10 <sup>-3</sup>                     |                   |

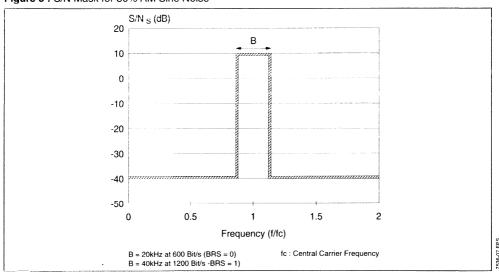

| BER6<br>BER7                         | Bit error rate with modulated sinusoidal noise Ns (1) | S+ Ns < 0.2V <sub>RMS</sub> , Ns = sine carrier<br>with 80% AM modul., f <sub>m</sub> = 1kHz,<br>See Figure 5<br>S <sub>min</sub> = 2mV <sub>RMS</sub> , BRS = 0<br>S <sub>min</sub> = 3mV <sub>RMS</sub> , BRS = 1 |          | TO THE PARTY OF TH | 10 <sup>-3</sup><br>10 <sup>-3</sup> |                   |

Note 1: This characteristic is guaranteed by correlation

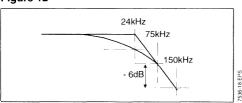

Figure 5: S/N Mask for 80% AM Sine Noise

# **FILTER TEMPLATES**

| Frequency (kHz)            | Test Conditions  |      | Amplitude (di | 3)   |

|----------------------------|------------------|------|---------------|------|

| r requericy (Kriz)         | rest conditions  | Min. | Тур.          | Max. |

| ECEIVE AND TRANSMIT FILTER | 3                |      |               |      |

| 54                         |                  |      |               | - 35 |

| 79.05                      |                  | - 4  | - 3           | - 2  |

| Ref 82.05                  | BRS = 0, CHS = 0 |      | 0             |      |

| 85.05                      |                  | - 4  | - 3           | - 2  |

| 123                        |                  |      |               | - 35 |

| 44.4                       |                  |      |               | - 35 |

| 65                         |                  | - 4  | - 3           | - 2  |

| Ref 67.46                  | BRS = 0, CHS = 1 |      | 0             |      |

| 69.93                      |                  | - 4  | - 3           | - 2  |

| 101.13                     |                  |      |               | - 35 |

| 47.57                      |                  |      |               | - 35 |

| 69.64                      |                  | - 4  | - 3           | - 2  |

| Ref 72.28                  | BRS = 1, CHS = 0 |      | 0             |      |

| 74.92                      |                  | - 4  | - 3           | - 2  |

| 108.36                     |                  |      |               | - 35 |

| 57.08                      |                  |      |               | - 35 |

| 83.57                      |                  | - 4  | - 3           | - 2  |

| Ref 86.74                  | BRS = 1, CHS = 1 |      | 0             |      |

| 89.91                      |                  | - 4  | - 3           | - 2  |

| 130.03                     |                  |      |               | - 35 |

| NTERMEDIATE FREQUENCY FIL  | .TER             |      |               |      |

| 1.2                        |                  |      |               | - 35 |

| 2.15                       |                  | - 5  | - 3           | - 2  |

| Ref 2.7                    | BRS = 0          |      | 0             |      |

| 3.25                       |                  | - 5  | - 3           | - 2  |

| 5.8                        |                  |      |               | - 35 |

| 2.4                        |                  |      |               | - 35 |

| 4.3                        |                  | - 5  | - 3           | - 2  |

| Ref 5.4                    | BRS = 1          |      | 0             |      |

| 6.5                        |                  | - 5  | - 3           | - 2  |

| 11.6                       |                  |      |               | - 35 |

# **PACKAGE MECHANICAL DATA**

28 PINS - PLASTIC CHIP CARRIER

| C28 EPS |

|---------|

| PMPLC   |

| Dimensions  | Millimeters |       |       | Inches |       |       |

|-------------|-------------|-------|-------|--------|-------|-------|

| Differsions | Min.        | Тур.  | Max.  | Min.   | Тур.  | Max.  |

| Α           | 12.32       |       | 12.57 | 0.485  |       | 0.495 |

| В           | 11.43       |       | 11.58 | 0.450  |       | 0.456 |

| D           | 4.2         |       | 4.57  | 0.165  |       | 0.180 |

| D1          | 2.29        |       | 3.04  | 0.090  |       | 0.120 |

| D2          | 0.51        |       |       | 0.020  |       |       |

| E           | 9.91        |       | 10.92 | 0.390  |       | 0.430 |

| е           |             | 1.27  |       |        | 0.050 |       |

| e3          |             | 7.62  |       |        | 0.300 |       |

| F           |             | 0.46  |       |        | 0.018 |       |

| F1          |             | 0.71  |       |        | 0.028 |       |

| G           |             |       | 0.101 |        |       | 0.004 |

| M           |             | 1.24  |       |        | 0.049 |       |

| M1          |             | 1.143 |       |        | 0.045 |       |

# **ST7536 APPLICATION NOTE**

AN653/0793

# **APPLICATION NOTE**

# ST7536

By Joël HULOUX

| SUMM             | ARY                                     | Page     |

|------------------|-----------------------------------------|----------|

| I.               | INTRODUCTION TO THE ST7536              | 2        |

| II.              | ST7536 DESCRIPTION                      | 2        |

| 111.             | ST7536 PIN DESCRIPTION                  | 3        |

| III.1            | POWER SUPPLY INPUT                      | 3        |

| III.2            | CHANNEL SELECTION                       | 4        |

| III.3            | CRYSTAL OSCILLATOR INPUT                | 4        |

| III.4            | AFCF STABILISATION                      | 4        |

| III.5            | AUTOMATIC LEVEL CONTROL INPUT           | 4        |

| III.6            | DATA INPUT AND OUTPUT                   | 5        |

| 111.7            | TEST INPUTS                             | 6        |

| III.8            | IFO/DEMI OUTPUT/INPUT                   | 6        |

| III.9            | TRANSMIT OUTPUT AND RECEIVE INPUT       | 6        |

| III.10           | Rx/Tx CONTROL INPUT                     | 6        |

| III.11           | RESET INPUT                             | 7        |

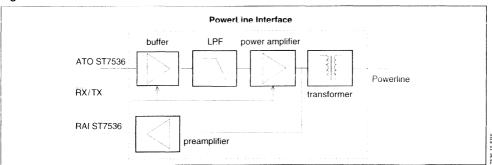

| IV.              | POWERLINE INTERFACE                     | 7        |

| IV.1             | BUFFER AND LOW PASS FILTER              | 7        |

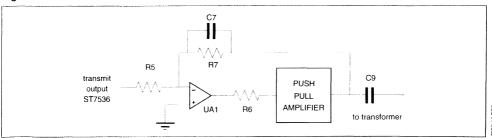

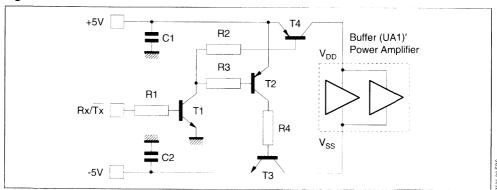

| IV.2             | POWER AMPLIFIER                         | 8        |

| IV.3             | TRANSFORMER                             | 9        |

| IV.4             | PREAMPLIFIER                            | 10       |

| IV.5             | POWER ON/OFF SWITCH                     | 10       |

| IV.6             | BUILDING UP THE POWERLINE INTERFACE     | 11       |

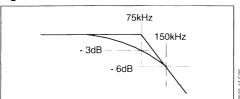

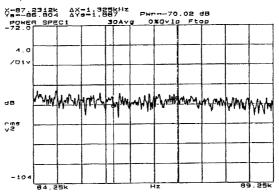

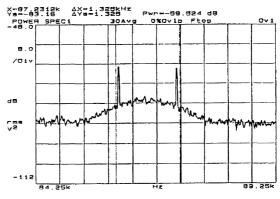

| IV.7             | PERFORMANCES OF THE POWERLINE INTERFACE | 11       |

| IV.7.1           | Power Consumption                       | . 12     |

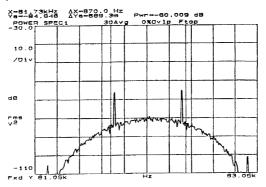

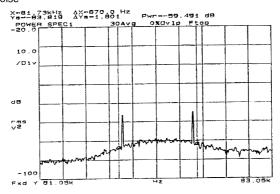

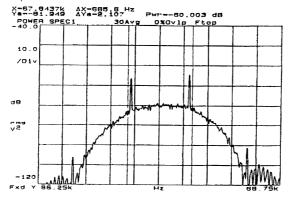

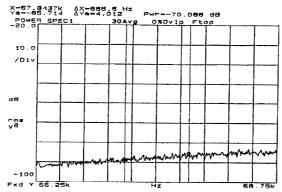

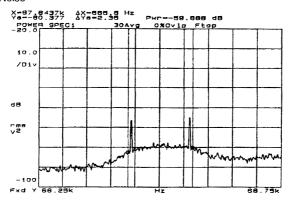

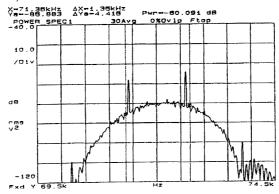

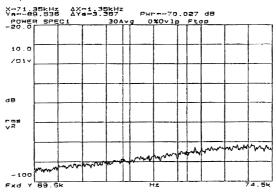

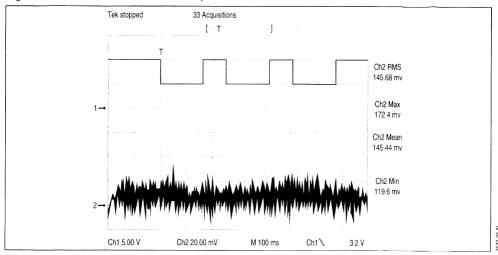

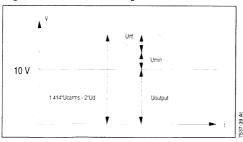

| IV.7.2           | Transmit Output                         | 12       |

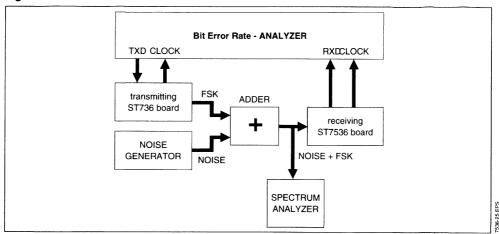

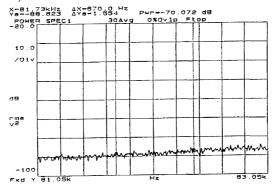

| IV.7.3<br>IV.7.4 | Receive Sensitivity                     | 13<br>15 |

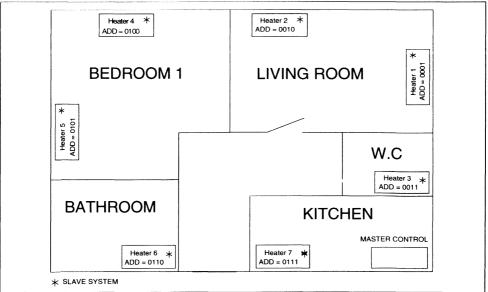

| V.               | HEATING CONTROL APPLICATIONS            | 15       |

|                  |                                         | 15       |

| V.1.             | INTRODUCTION                            | 16       |

| V.2.             |                                         |          |

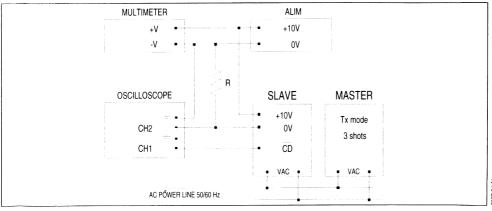

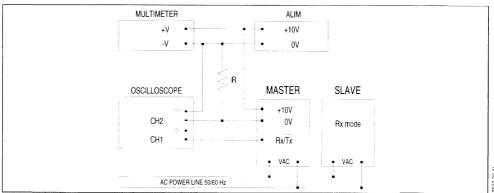

| V.3.             | HARDWARE                                | 16       |

| V.4.             | SLAVE                                   | 16       |

| V.5.             | MASTER                                  | 17       |

| V.6.             | SOFTWARE                                | 17       |

| V.7.             | PROTOCOL                                | 18       |

| V.8.             | APPLICATIONS SOFTWARE                   | 20       |

|                  |                                         |          |

# I - INTRODUCTION TO THE ST7536

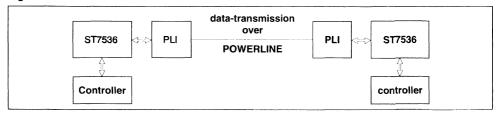

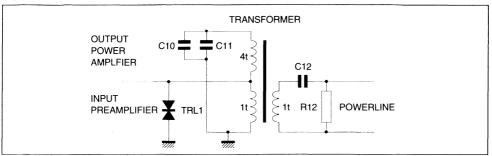

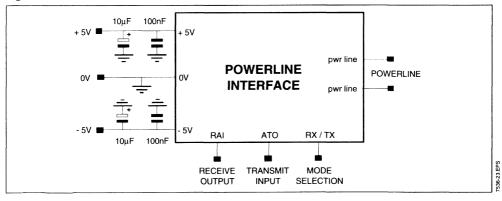

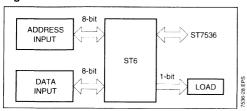

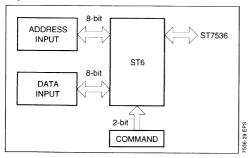

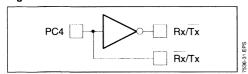

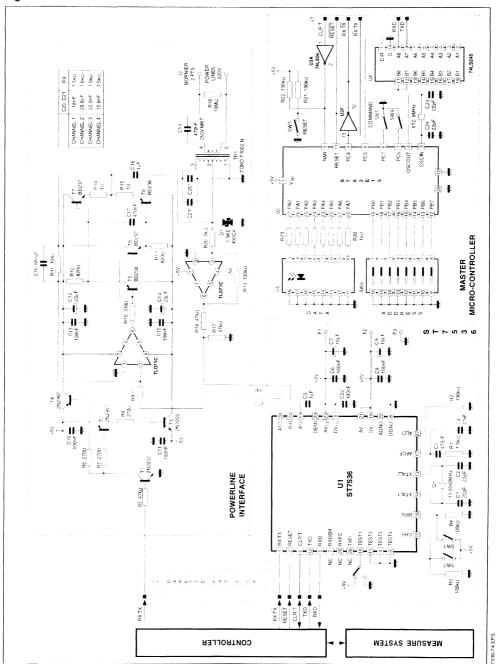

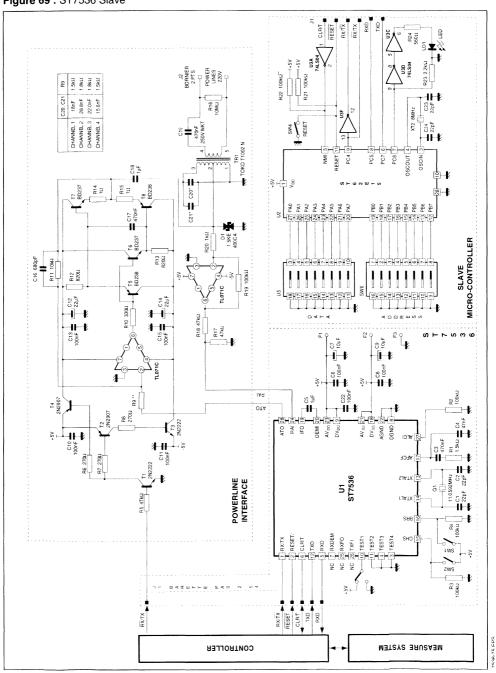

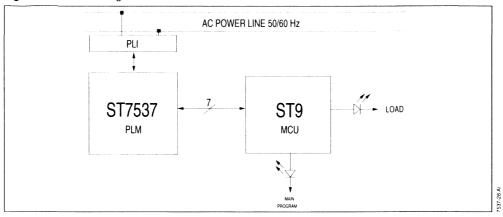

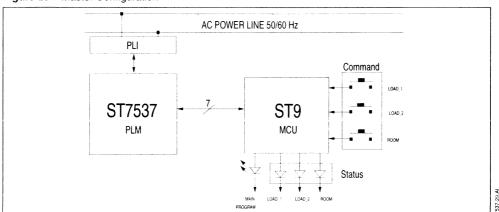

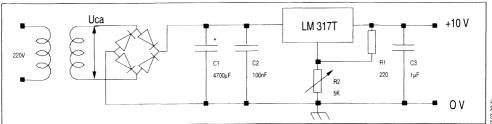

The ST7536 is a half duplex synchronous FSK-modem, and has been designed to operate on power-line networks. For a complete communication system, a micro-controller and a powerline-interface (PLI) are needed (see Figure 1).

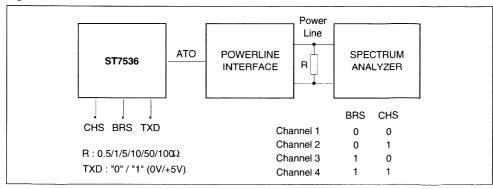

Such a system is able to transmit and receive on 4 different channels with 2 different data rates (600 and 1200 baud). The baudrate (BRS) and channel (CHS) selection is made, according to the table 1:

Table 1

| BRS | снѕ | Bitrate | Xmit Freq<br>(KHz)<br>TxD = 1 | Xmit Freq<br>(KHz)<br>TxD = 0 |

|-----|-----|---------|-------------------------------|-------------------------------|

| 0   | 0   | 600     | 81.75                         | 82.35                         |

| 0   | 1   | 600     | 67.20                         | 67.80                         |

| 1   | 0   | 1200    | 71.40                         | 72.60                         |

| 1   | 1   | 1200    | 85.95                         | 87.15                         |

The ST7536 is a half duplex modem, as it has two operation modes; receive or transmit data. The mode selection is made with a Rx/Tx control input.

Data input and output are related to the clock signal; it's a synchronous modem. This clock signal is generated by the ST7536.

Only a few external components have to be added for full operation of the ST7536: a crystal, four resistors and five capacitors.

# **II - ST7536 DESCRIPTION**

The ST7536 is a single chip modem; all the electrical circuits needed for a complete modem are inside the chip. The modem is available in 28 pins PLCC (see Figure 2).

In transmit mode the Transmit Data (TXD) is sampled on the positive edge of the clock (CLR/T). Then the data enters the FSK modulator. The frequency on which this modulator operates is set by the time base and control logic. In normal operation the multiplexer (MUX) selects the FSK modulator signal to be send to the transmit filter. This filter is a switched capacitor band-pass filter.

The time base and control logic uses the Automatic Frequency Control (AFC) to set this filter at the transmit frequency, corresponding to the selected channel. After filtering, the transmit signal is sent to an Automatic Level Control (ALC). This control is used to overcome problems with line impedance variations. The powerlines on which the modem has to operate, have variations in their line characteristics, which are very frequent and totally unpredictable. The automatic level control uses a feed back signal (ALCI) from the powerline interface to adjust the transmit output (ATO).

In receive mode the signal enters the chip on the Receive Analog Input (RAI). The received signal is filtered in the receive band-pass filter. It's just like the transmit filter, a switched capacitor filter. The automatic frequency control is used to set it on the right frequency. After being amplified the signal is down converted and filtered in the intermediate frequency band-pass filter. The resulting signal is sent to the FSK demodulator. The coupling of the intermediate frequency filter output (IFO) to the FSK DEModulator Input (DEMI) is made by an external capacitor which cancels an eventual offset voltage. A clock recovery circuit extracts the receive clock (CLR/T) from the demodulated output (RXDEM) of the FSK demodulator. Synchronous received data (RXD) is delivered on the positive edge of the clock.

A time base section delivers all the internal clock signals from a crystal oscillator running at 11.0592 MHz. The crystal is connected between the XTAL1 and XTAL2 pins. It is also possible to provide directly a clock signal on XTAL1 instead of using a crystal.

To debug the chip and test external circuits the ST7536 provides some test options. The transmit band-pass filter can be observed using a direct input on the filter. This input (TXFI) is selected by the multiplexer if TEST4 = 1. The Receive bandpass Filter Output (RXFO) is provided at pin 25 Finally the clock recovery can be observed when TEST1 = 1. In this case the TEST3 input gives a direct input to the clock recovery block.

Figure 1

Figure 2: Block Diagram

# **III - ST7536 PIN DESCRIPTION**

The pin decription is not given in numerical order, but the pins are described in relation with their function and consequently sometimes with other pins.

- power supply input

- channel selection

- crystal oscillator input

- AFCF stabilisation

- automatic level control input

- data input and output

- test inputs

- IFO/DEMI output/input

- transmit output and receive input

- Rx/Tx control input

- reset input

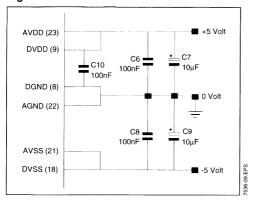

# III.1 - Power Supply Input

- pin 8 (DGND) : Digital ground (0V)

- pin 9 (DV<sub>DD</sub>) : Digital positive supply

voltage (+5V)

- pin 18 (DVss) : Digital negative supply

voltage (-5V)

- pin 21 (AV<sub>SS</sub>) : Analog negative supply

voltage (-5V)

- pin 22 (AGND): Analog ground (0V)

- pin 23 (AV<sub>DD</sub>) : Analog positive supply

voltage (+5V)

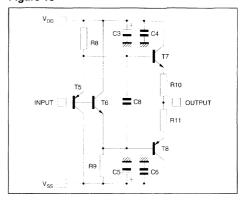

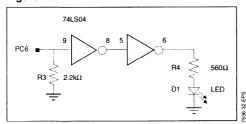

Internally the ST7536 has separated power supplies: the digital and analog circuits are separated. Externally the power supplies should be connected together. For decoupling, both the positive and negative supplies are decoupled with 2 capacitors. C6 and C7 decouple the positive, C8 and C9 the negative supplies. For proper operation the digital positive supply voltage should be decoupled with a capacitor (C10) mounted close to pin 9. C6,C8 and C10 are 100nF/16V ceramic capacitors, C7 and C9  $10\mu$ F/16V tantal capacitors (see Figure 3).

Figure 3

# III.2 - Channel Selection

- pin 15 (CHS) : Channel selection input

- pin 16 (BRS) : Baudrate selection input

Both inputs are digital inputs (0/+5V). The ST7536 operates with two bitrates: 600 and 1200 baud. These bitrates are selected with pin 16 (BRS). For both bitrates the ST7536 offers two channels, which are selected with pin 15 (CHS).

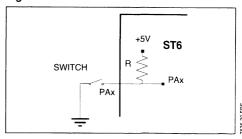

A logical "0" is represented by 0V, a "1" by +5V. R1 and R2 are pull-down resistors, creating a logical "0". Closing a switch gives a "1". The selection is made according to table I.

Figure 4

# III.3 - Crystal Oscillator Input

- pin 13 (XTAL2) : Crystal oscillator output

- pin 14 (XTAL1) : Crystal oscillator input

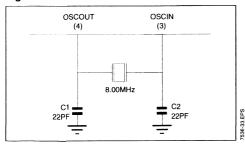

The internal crystal oscillator of the ST7536 needs an external crystal. This one should be a 11.0592MHz crystal. Two capacitors (C1 and C2) have to be added for proper operation. They are typically 22pF/10V ceramic capacitors.

It is also possible to connect directly a clock signal to the oscillator input, in this case the crystal and the capacitors should be removed. On the application board this option is not used. The ST7536 clock signal is the time reference of the system.

Figure 5

# III.4 - AFCF Stabilisation

- pin 17 (AFCF) : Automatic frequency control output

In the ST7536 an automatic control section adjusts the central frequency of the receive and transmit band-pass filters. The stability of this section has to be ensured with an external RC network.

Figure 6

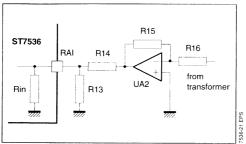

# III.5 - Automatic Level Control Input

- pin 27 (ALCI) : Automatic level control input

The output stage of the transmit path consists of an automatic level control (ALC). It offers the possibility to keep the output voltage of the power amplifier independent of variations of the powerline network. The impedance of these networks can be anywhere in the range of 5 -  $100\Omega$ . If the impedance of the powerline changes, the output of the amplifier will change. With the ALC input it is possible to correct these output variations. To control the output of the powerline interface a feed-back signal is

needed. This signal is sent through an amplifier. The automatic level control can decrease the maximum transmit output in 32 steps of 0.84dB. The gain range is 0dB  $\rightarrow$  -26dB. A peak detection is done on the signal presented on the ALCInput and the ALC compares it to two reference voltages, VT1 (1.87V) and VT2 (2.12V).

If max. VALCI < VT1 the next gain is increased by 0.84dB.

If VT1 < max. VALCI < VT2 there is no gain change. If VT2 < max. VALCI the next gain is decreased by 0.84dB.

The gain of the feed-back amplifier is such that the feed-back signal peak voltage falls between  $V_{T1}$  and  $V_{T2}$ .

# Example:

The wanted interface output voltage is 0.5V(peak).

For a 0.5V output peak voltage

$$G = \frac{V_{out peak}}{\left(\frac{V_{T1} + V_{T2}}{2}\right)} = \frac{0.5}{2} = 4 \text{ (12dB)}.$$

Then the feed-back amplifier should have a gain of 4x (= +12dB). The ST7536 starts up. VALCI = 0V (VALCI < VT1). The ATO output is increased with a gain of +0.84dB. On a certain moment the output voltage over the powerline will become 0.5 V(peak). This signal is amplified to 2.0 V(peak). Then the ALC stops increasing the ATO output. which will remain at its actual level. If the line impedance increases, the power amplifier of the interface might deliver more output voltage. If the output voltage of this amplifier increases, the ALCI voltage will be higher than VT2. The ALC will then immediately decrease the ATO output. And so the output of the interface can be made independent of impedance variations of the powerline.

Of course this will operate only if the power ampli-

fier in the interface is able to drive all the impedances at the required output voltage. Let's say the impedance of the line becomes  $0.1\Omega$ . The ALC will increase the output of the ATO. But if the power amplifier is not able to drive such low impedances, the only result will be an output signal with a large distortion. Therefore on the application board the ALCInput is set at 0V with a resistor (R4). The ATO will be always at maximum output (1.25 Vrms). The powerline interface has been designed to drive all impedances from  $0.5 - 100\Omega$  with this input. To be able to do some experiments with the ALC, a resistor is used to set the ALCI at 0V. It gives the possibility to inject a signal on the ALCI. This would not have been possible if on the printed circuit board a short circuit to ground had been made (see Figure 7)

# III.6 - Data Input and Output

- pin 5 (RxD) : Synchronous receive data

output

pin 6 (CLR/T) : Receive and transmit clockpin 7 (RxDEM) : Demodulated data output

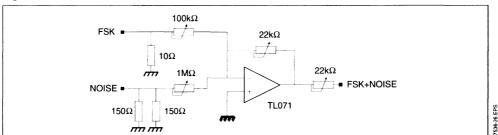

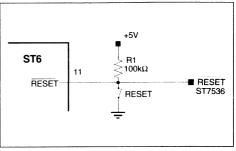

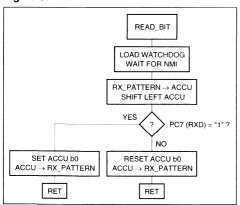

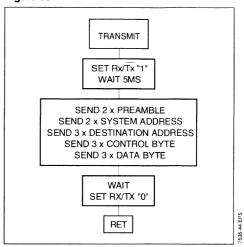

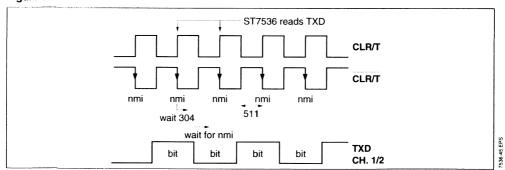

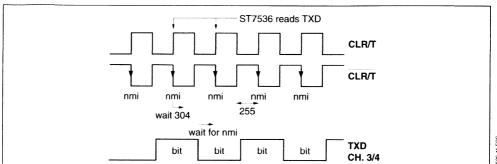

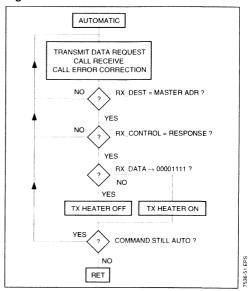

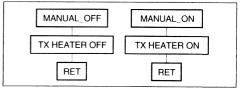

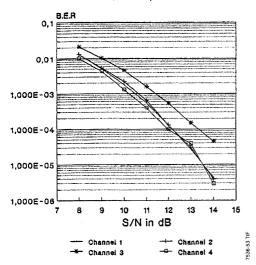

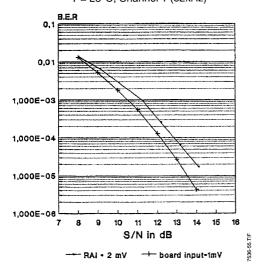

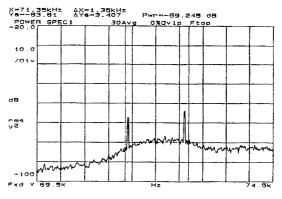

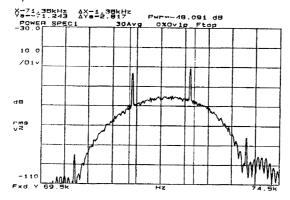

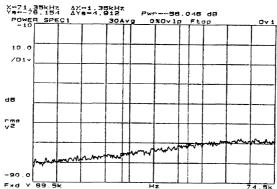

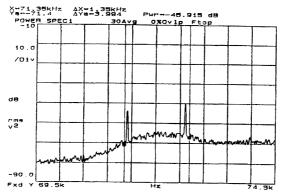

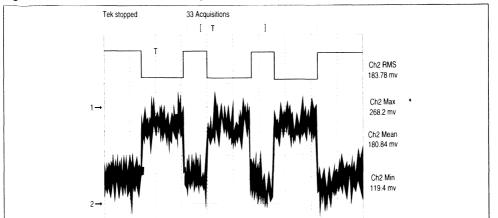

- pin 12 (TxD) : Transmit data input